1. Praktek Umum

Ing desain PCB, supaya desain papan sirkuit frekuensi dhuwur luwih cukup, kinerja anti-gangguan luwih, kudu dianggep saka aspèk ing ngisor iki:

(1) Pilihan sing cukup saka lapisan Nalika nuntun papan sirkuit frekuensi dhuwur ing desain PCB, bidang utama ing tengah digunakake minangka daya lan lapisan lemah, kang bisa muter peran shielding, èfèktif nyuda inductance parasitic, shorten dawa garis sinyal, lan nyuda interferensi salib antarane sinyal.

(2) Mode Routing Mode Routing kudu selaras karo 45 ° Angle ngowahi utawa busur ngowahi, kang bisa ngurangi emisi sinyal frekuensi dhuwur lan bebarengan kopling.

(3) Dawane kabel Sing luwih cendhek dawa kabel, luwih apik. Sing luwih cendhek jarak paralel antarane rong kabel, luwih apik.

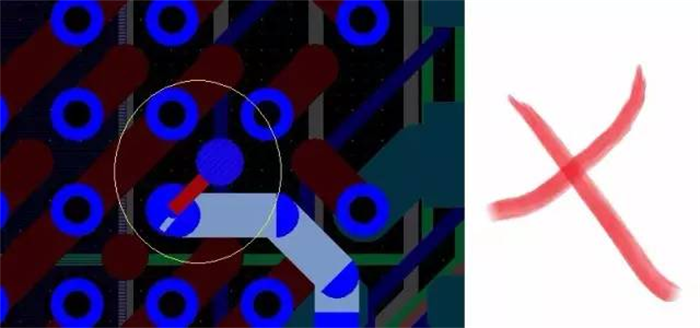

(4) Jumlah liwat bolongan Sing kurang nomer liwat bolongan, sing luwih apik.

(5) Arah kabel interlayer Arah kabel interlayer kudu vertikal, yaiku, lapisan ndhuwur horisontal, lapisan ngisor vertikal, supaya bisa nyuda gangguan antarane sinyal.

(6) Lapisan tembaga tambah lapisan tembaga grounding bisa nyuda gangguan ing antarane sinyal.

(7) Gawan saka Processing baris sinyal penting, Ngartekno bisa nambah kemampuan anti-gangguan sinyal, mesthi, bisa uga Gawan Processing sumber gangguan, supaya ora bisa ngganggu sinyal liyane.

(8) Kabel sinyal ora rute sinyal ing puteran. Sinyal rute ing mode chain Daisy.

2. Wiring prioritas

Prioritas garis sinyal utama: sinyal cilik analog, sinyal kacepetan dhuwur, sinyal jam lan sinyal sinkronisasi lan kabel prioritas sinyal kunci liyane

Kapadhetan prinsip pisanan: Mulai wiring saka sambungan paling Komplek ing Papan. Mulai wiring saka wilayah paling padhet kabel saka Papan

Titik sing kudu dicathet:

A. Coba nyedhiyakake lapisan kabel khusus kanggo sinyal kunci kayata sinyal jam, sinyal frekuensi dhuwur lan sinyal sensitif, lan njamin area loop minimal. Yen perlu, kabel prioritas manual, shielding lan nambah jarak safety kudu diadopsi. Priksa kualitas sinyal.

b. Lingkungan EMC ing antarane lapisan daya lan lemah ora apik, mula sinyal sing sensitif marang gangguan kudu dihindari.

c. Jaringan kanthi syarat kontrol impedansi kudu disambungake kanthi kabel sabisa miturut syarat dawa lan jembar garis.

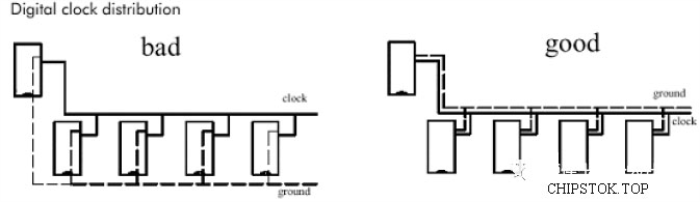

3, kabel jam

Garis jam minangka salah sawijining faktor paling gedhe sing mengaruhi EMC. Nggawe kurang bolongan ing baris jam, supaya mlaku karo garis sinyal liyane sabisa, lan adoh saka garis sinyal umum supaya gangguan karo garis sinyal. Ing wektu sing padha, sumber daya ing Papan kudu nyingkiri kanggo nyegah gangguan antarane sumber daya lan jam.

Yen ana chip jam khusus ing Papan, iku ora bisa pindhah ing baris, kudu glethakaken ing tembaga, yen perlu, bisa uga khusus kanggo sawijining tanah. Kanggo akeh osilator kristal referensi chip, osilator kristal iki ora kudu ana ing sangisore garis, kanggo ngisolasi tembaga.

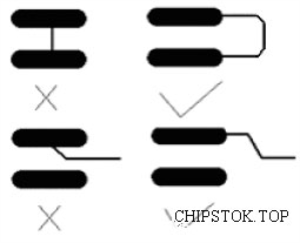

4. Garis ing sudhut tengen

Kabel sudut tengen umume dibutuhake supaya ora ana kahanan ing kabel PCB, lan meh dadi salah sawijining standar kanggo ngukur kualitas kabel, mula kepiye pengaruh kabel sudut tengen ing transmisi sinyal? Ing asas, nuntun sudhut tengen bakal nimbulaké jembaré baris saka baris transmisi kanggo ngganti, asil ing discontinuity impedansi. Nyatane, ora mung tengen Angle nuntun, ton Angle, akut Angle nuntun bisa nimbulaké owah-owahan impedansi.

Pengaruh rute sudut tengen ing sinyal utamane dibayangke ing telung aspek:

Kaping pisanan, sudhut bisa padha karo beban kapasitif ing jalur transmisi, nyuda wektu munggah;

Kapindho, impedansi discontinuity bakal nimbulaké bayangan sinyal;

Katelu, EMI diprodhuksi dening tip Angle tengen.

5. Sudut Akut

(1) Kanggo saiki frekuensi dhuwur, nalika titik balik saka kabel presents Angle tengen utawa malah Angle leukemia, cedhak sudhut, Kapadhetan flux Magnetik lan kakiyatan medan listrik sing relatif dhuwur, bakal radiation gelombang elektromagnetik kuwat, lan induktansi kene bakal relatif gedhe, induktif bakal luwih gedhe tinimbang Angle obtuse utawa dibunderaké Angle.

(2) Kanggo kabel bis saka sirkuit digital, sudhut wiring iku obtuse utawa dibunderaké, area wiring relatif cilik. Ing kondisi spasi baris padha, total spasi baris njupuk munggah 0,3 kaping kurang jembaré saka giliran Angle tengen.

6. Nuntun diferensial

Cf. kabel diferensial lan cocog impedansi

Sinyal Diferensial digunakake luwih akeh ing desain sirkuit kacepetan dhuwur, amarga sinyal sing paling penting ing sirkuit tansah nggunakake struktur diferensial. Definisi: Ing basa Inggris sing prasaja, tegese driver ngirim loro sinyal sing padha, ngowahi, lan panrima nemtokake manawa negara logis "0" utawa "1" kanthi mbandhingake prabédan antarane rong voltase. Pasangan sing nggawa sinyal diferensial diarani rute diferensial.

Dibandhingake karo nuntun sinyal siji-rampung biasa, sinyal diferensial nduweni kaluwihan sing paling jelas ing telung aspek ing ngisor iki:

a. Kemampuan anti-gangguan kuwat, amarga kopling antarane loro kabel diferensial apik banget, nalika ana gangguan gangguan saka njaba, iku meh gegandhengan karo loro baris ing wektu sing padha, lan panrima mung peduli prabédan antarane loro sinyal, supaya gangguan mode umum saka njaba bisa rampung dibatalake.

b. bisa efektif nyandhet EMI. Kajaba iku, amarga polaritas loro sinyal ngelawan, medan elektromagnetik sing dipancarake bisa mbatalake siji liyane. Sing nyedhaki kopling, kurang energi elektromagnetik sing dibebasake menyang jagad njaba.

c. Posisi wektu sing tepat. Wiwit owah-owahan ngoper sinyal diferensial dumunung ing persimpangan saka loro sinyal, ora kaya sinyal siji-rampung biasa kang gumantung ing voltase batesan dhuwur lan kurang, impact saka teknologi lan suhu cilik, kang bisa nyuda kasalahan ing wektu lan luwih cocok kanggo sirkuit karo sinyal amplitudo kurang. LVDS (sinyal diferensial tegangan rendah), sing populer saiki, nuduhake teknologi sinyal diferensial amplitudo cilik iki.

Kanggo insinyur PCB, sing paling penting yaiku kanggo mesthekake yen kaluwihan rute diferensial bisa digunakake kanthi lengkap ing rute sing nyata. Mbok menawa kontak karo wong Layout bakal ngerti syarat umum saka nuntun diferensial, yaiku, "padha dawa, jarak sing padha".

Dawane padha kanggo mesthekake yen loro sinyal diferensial njaga polaritas ngelawan ing kabeh wektu lan ngurangi komponen umum-mode. Equidistance utamane kanggo mesthekake yen impedansi prabédan konsisten lan nyuda bayangan. "Minangka cedhak bisa" kadhangkala syarat kanggo nuntun diferensial.

7. Snake line

Garis Serpentine minangka jinis Layout sing asring digunakake ing tata letak. Tujuan utamane yaiku nyetel wektu tundha lan nyukupi syarat desain wektu sistem. Wangsulan: Bab ingkang pisanan Desainer kudu éling iku kabel ula-kaya bisa numpes kualitas sinyal lan ngganti wektu tundha transmisi, lan kudu nyingkiri nalika wiring. Nanging, ing desain nyata, kanggo mesthekake wektu nyekeli cekap saka sinyal, utawa kanggo ngurangi wektu nutup kerugian antarane klompok padha sinyal, iku asring perlu kanggo sengaja angin.

Titik sing kudu dicathet:

Pasangan saka garis sinyal diferensial, umume garis podo, minangka sethitik sabisa liwat bolongan, kudu punched, kudu loro baris bebarengan, supaya entuk impedansi cocog.

Klompok bus kanthi atribut sing padha kudu diarahake kanthi sisih sabisa kanggo entuk dawa sing padha. Bolongan anjog saka pad patch minangka adoh saka pad sabisa.

Wektu kirim: Jul-05-2023